┃ 直播详情 ┃

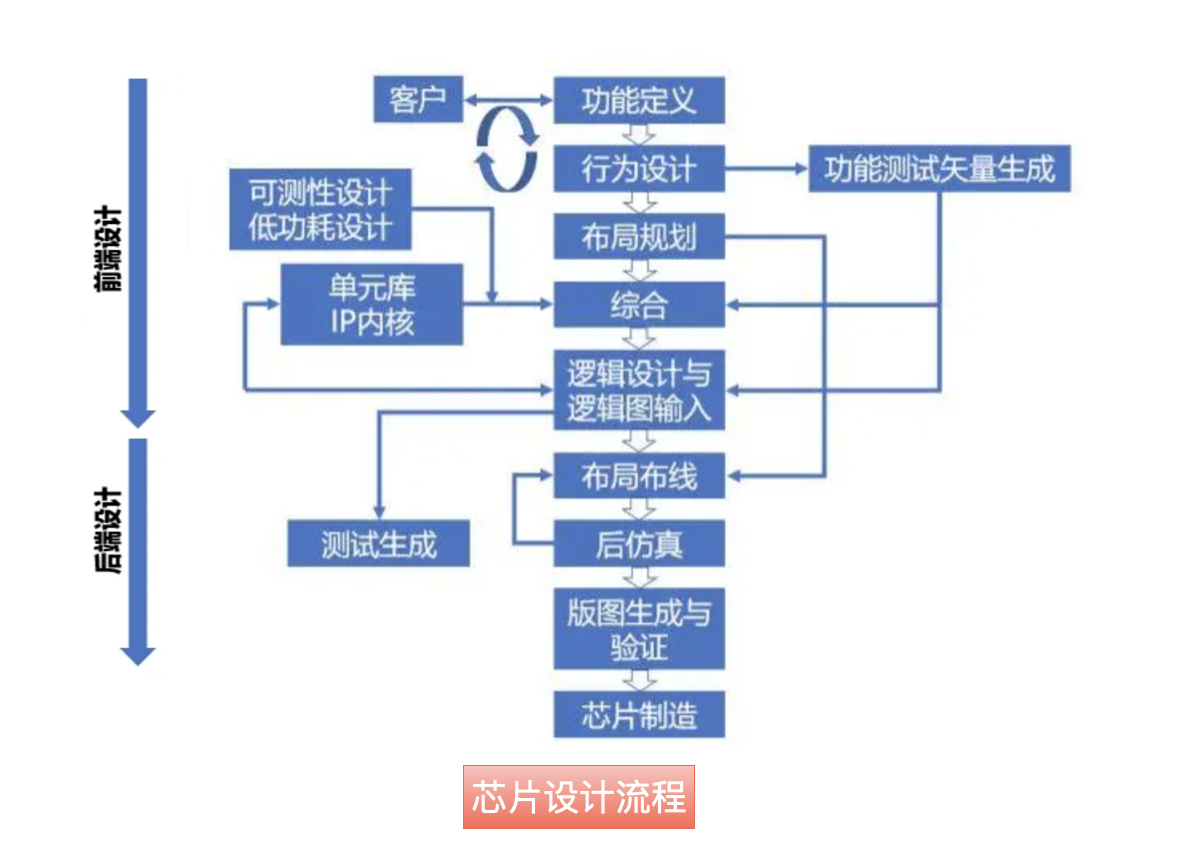

逻辑综合是芯片前端设计中最重要环节之一,其过程是将行为描述的电路、RTL级的电路转换到门级,其目的在于决定电路门级结构、寻求时序与面积的平衡、寻求功耗与时序的平衡以及增强电路的测试性。这个环节是国外EDA巨头的优势领域,也是本土EDA急需突破的关键核心技术。

近年来,随着芯片设计规模不断扩大、工艺日益演进以及性能优化日益严格,逻辑综合也面临不断增加的挑战,如算法效率挑战——即在逻辑综合过程中涉及的布尔优化、映射等步骤多为NP-hard问题,寻找有效的启发式算法以提高求解效率。

又如随着AI技术的发展,逻辑综合如何整合AI算法提升效率?以及如何与云计算整合,如何与IP协同,本土EDA如何实现全流程覆盖?等等诸多挑战。

不过近年来在政府和资本的支持下,本土EDA茁壮成长,已经在EDA各个重要节点实现全面突破,在逻辑综合领域,本土EDA发挥产研结合的优势也获得了突破!为了让大家了解本土EDA在逻辑综合领域的突破,5月29日晚19点,我们特别邀请了雷娜科技CEO杨晓燕、宁波大学教授储著飞做客贸泽电子芯英雄联盟直播间,与大家围绕“本土EDA逻辑综合的突破与未来发展”展开讨论,欢迎预约围观!

直播时间:2024年5月29日 19:00~20:30

直播主题:本土EDA逻辑综合的突破与未来发展

▶ 本期看点

① EDA逻辑综合发展历史

② 本EDA逻辑综合发展现状

③ 本土逻辑综合该如何突破?

④ 结合雷娜科技的新品分析本土逻辑综合突破以及未来发展

▶ 嘉宾介绍

分享嘉宾————杨晓燕

雷娜科技CEO,深耕集成芯片大规模数字逻辑综合工具研发二十多年。2022年以业界顶级专家身份成为杭州电子科技大学特聘教授、博士生导师。在全球顶级EDA公司工作二十余年期间,主导研发首款物理综合与逻辑综合融合的DCTopographical /DC Graphical产品、领导开发目前仍占据领先地位的数字 RTL2GDSII EDA工具Fusion Compiler,深度参与服务全球先进的高端芯片设计厂家数代CPU/AI芯片综合设计芯片项目。目前主导开发雷娜科技的新一代数字芯片设计EDA软件,第一款完全自主知识产权的逻辑综合产品RainaSynth已于2024年一季度在国内发布。

研究方向包括:分布式逻辑综合算法、基于人工智能的逻辑综合算法、GPU加速的逻辑综合算法、基于机器学习的布局算法、时序驱动布局算法等。

分享嘉宾————储著飞

宁波大学信息科学与工程学院教授,博士生导师,宁波大学"包玉刚卓越学者"。研究方向为集成电路设计自动化(EDA),包括逻辑综合与优化,物理设计,逻辑等价性验证等。主持国家自然科学基金项目3项,省部级项目2项,在开源平台开源了自研的逻辑综合工具ALSO。研究成果获得浙江省技术发明二等奖1次,宁波市科学技术进步奖一等奖2次,CCFDAC最佳论文奖。

主持人————张国斌

电子创新网创始人兼CEO ,

西安电子科技大学电子工程专业毕业,半导体领域知名KOL。

有多年的半导体媒体内容与运营经验,撰写过大量产业分析文章。(微信号:18676786761)

▶ 直播福利

1、预报名奖:20元京东E卡(10名)

通过小鹅通平台填写预约信息,我们将在所有预报名的用户中随机抽取10名,送出价值20元的京东E卡。

2、优秀提问奖:30元京东E卡(5名)

直播期间,在小鹅通平台评论区参与提问,随机抽取5名提问用户,送出价值30元的京东E卡。

注意事项

请预约直播的用户填写正确的邮箱,我们将通过邮件的方式联系获奖者。如因用户信息填写不全无法发放奖励的,自动取消获奖资格,随机抽取其他人员。直播福利的最终解释权归属电子创新网所有。

扫描以下二维码进行预约报名吧!

欢迎扫码加入直播交流群,和同行进行深入沟通交流!